JTAG

Joint Test Action Group

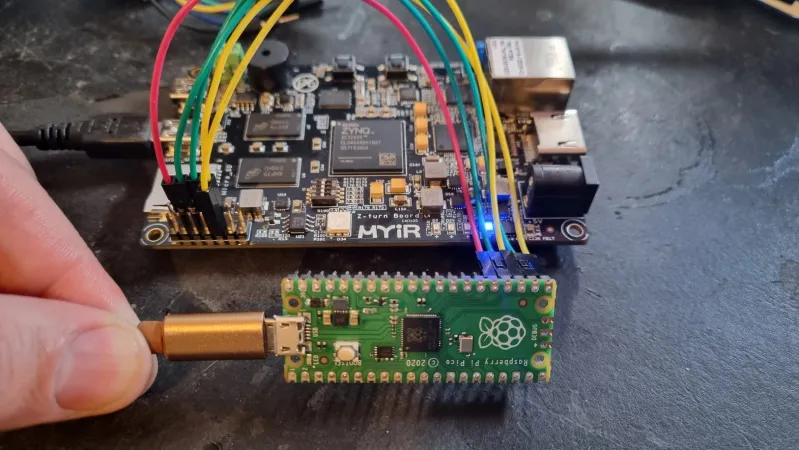

오늘의 주제는 JTAG이다. 하드웨어에서 직접 펌웨어를 추출하는 작업을 준비하며 접한 새로운 용어인데, 현재로서는 작업 대상이 될 가능성은 낮아 보인다. 다만 여전히 중요한 분석 방법 중 하나로 판단되므로, 이번 기회에 한번 조사해보고자 한다.

1. JTAG의 개요

1.1 JTAG의 정의와 역할

JTAG(Joint Test Action Group) 은 전자 회로 및 칩의 디버깅과 테스트를 목적으로 설계된 표준 인터페이스이다. 주로 임베디드 시스템과 마이크로컨트롤러에서 사용되며, 하드웨어 레벨에서 디버깅, 펌웨어 업로드, 보드 테스트 등을 가능하게 한다.

주요 역할

- 디버깅: CPU 레지스터나 메모리와 같은 시스템 내부 상태를 직접 확인하고 수정 가능

- 펌웨어 업로드: 플래시 메모리에 새로운 펌웨어를 안전하게 로드

- 하드웨어 테스트: 보드의 배선 연결 상태 및 각 부품의 기능을 확인

- 데이지 체인 지원: 여러 장치를 하나의 인터페이스로 연결해 동시 테스트 가능

JTAG은 설계 단계에서부터 제조 및 유지보수 단계까지 전 과정을 지원하는 중요한 기술로 자리 잡고 있다.

1.2 JTAG의 역사와 발전

JTAG의 역사는 1980년대 후반으로 거슬러 올라간다. 당시 전자 부품의 집적도가 높아지면서 기존의 테스트 방법으로는 내부 회로를 충분히 검증할 수 없었다. 이에 따라 전 세계 반도체 제조사들이 공동으로 JTAG 표준을 개발하게 되었다.

역사적 발전 과정

- 1985년: 테스트 효율성을 높이기 위해 JTAG 컨소시엄이 결성

- 1990년: IEEE 1149.1 표준으로 공식 채택되며, JTAG이 반도체 및 하드웨어 업계에서 널리 사용되기 시작

- 2000년대 이후: JTAG은 단순 테스트를 넘어 디버깅 및 프로그래밍 도구로 확장. OpenOCD와 같은 오픈소스 JTAG 도구가 등장하며 개발자 친화적 환경이 조성

- 현재: IoT, 임베디드 시스템 등 다양한 영역에서 JTAG이 필수 기술로 자리 잡음

1.3 JTAG 표준(IEEE 1149.1)과 기본 원칙

JTAG 표준: IEEE 1149.1

JTAG은 IEEE(Institute of Electrical and Electronics Engineers)에서 제정한 1149.1 표준에 따라 동작한다. 이 표준은 주로 Boundary Scan Test(BST) 라는 개념을 기반으로 설계되었다. Boundary Scan Test는 칩 내부와 보드 간의 연결 상태를 테스트하는 기술이다.

기본 원칙

-

Boundary Scan 셀

- 각 핀에 Boundary Scan 셀이 연결되어, 데이터 흐름을 제어하고 검증

- 외부 핀뿐만 아니라 내부 회로도 테스트 가능

-

TAP(테스트 액세스 포트)

- JTAG 인터페이스의 핵심으로, 4~5개의 핀(TDI, TDO, TCK, TMS, 선택적 TRST)으로 구성

- TAP 상태 머신을 통해 다양한 테스트 및 디버깅 작업 수행

-

데이지 체인 구조

- 여러 장치를 직렬 연결하여 하나의 JTAG 포트로 제어 가능

- 대규모 회로의 효율적인 테스트를 지원

Boundary Scan 셀의 동작 원리

| 명령어 | 기능 | 활용 예 |

|---|---|---|

| BYPASS | 데이터 패스 없이 테스트 신호 전달 | 연결된 장치 중 특정 장치를 무시. |

| EXTEST | 외부 회로 테스트 | 보드 배선 연결 상태 검증. |

| SAMPLE/SCAN | 내부 레지스터 값 읽기 | 디버깅 중 내부 상태 확인. |

| IDCODE | 장치 고유 ID 반환 | 장치 식별 및 인증. |

JTAG 표준은 하드웨어 디버깅 및 테스트에서 필수적인 기술로, 높은 신뢰성과 정확성을 제공한다.

2. JTAG의 아키텍처와 동작 원리

2.1 TAP(테스트 액세스 포트)와 상태 머신

TAP의 정의와 역할

TAP(Test Access Port) 는 JTAG 인터페이스의 핵심 요소로, 테스트 및 디버깅 작업을 수행하기 위한 물리적 포트와 상태 제어 논리를 제공한다. TAP는 4~5개의 핀으로 구성되며, 장치 내부의 Boundary Scan 셀과 상호작용하여 데이터를 읽고 쓰거나 장치 상태를 제어한다.

TAP 상태 머신

TAP는 상태 머신(State Machine) 으로 동작하며, IEEE 1149.1 표준에 따라 16개의 고정 상태를 가진다. TAP 상태 머신은 TCK(테스트 클럭)과 TMS(테스트 모드 선택) 신호를 사용해 상태 전환을 제어한다.

| 상태 | 기능 | 설명 |

|---|---|---|

| Test-Logic-Reset | 초기 상태 | JTAG 초기화 및 비활성화 상태. |

| Run-Test/Idle | 기본 대기 상태 | 데이터 입력 대기 상태. |

| Select-DR-Scan | 데이터 레지스터 스캔 선택 | 데이터 관련 작업 수행 준비. |

| Select-IR-Scan | 명령어 레지스터 스캔 선택 | 명령어 관련 작업 수행 준비. |

| Shift-DR/Shift-IR | 레지스터 데이터를 시프트 인 또는 시프트 아웃 | 레지스터 값을 읽거나 씀. |

| Update-DR/Update-IR | 레지스터에 변경된 값을 업데이트 | 데이터/명령어 변경 적용. |

TAP 상태 머신은 JTAG 명령어 처리 및 데이터 흐름 제어를 담당하며, 정확한 상태 전환이 이루어져야 올바르게 동작한다.

2.2 JTAG 핀 구성 (TDI, TDO, TCK, TMS 등)

주요 핀 구성

JTAG 인터페이스는 4~5개의 주요 핀으로 구성된다. 각 핀은 특정한 역할을 담당하며, JTAG 프로토콜의 데이터 흐름과 제어를 구현한다.

| 핀 이름 | 역할 | 설명 |

|---|---|---|

| TDI | 테스트 데이터 입력 (Test Data In) | JTAG 장치로 데이터와 명령어를 입력. |

| TDO | 테스트 데이터 출력 (Test Data Out) | JTAG 장치에서 데이터를 출력. |

| TCK | 테스트 클럭 (Test Clock) | TAP 상태 전환 및 데이터 시프트를 위한 클럭 신호. |

| TMS | 테스트 모드 선택 (Test Mode Select) | TAP 상태 머신의 상태를 제어. |

| TRST | 테스트 리셋 (Test Reset) (선택적) | TAP 상태 머신을 초기화하는 선택적 핀. |

데이터 흐름

- TDI를 통해 입력된 데이터는 TAP 상태 머신을 통해 처리되고, 결과가 TDO로 출력된다.

- TCK 신호는 데이터 전송과 상태 변화를 동기화하며, TMS는 TAP 상태 머신의 동작 모드를 결정한다.

예시

데이터 시프트 및 레지스터 업데이트는 다음과 같은 방식으로 이루어진다:

- TDI를 통해 레지스터에 데이터 입력

- TCK 신호에 맞춰 데이터가 이동

- TDO에서 데이터를 읽어 결과 확인

2.3 데이지 체인 연결 방식과 활용

데이지 체인이란?

데이지 체인(Daisy Chain)은 여러 JTAG 호환 장치를 직렬로 연결하는 구조를 말한다. 이 방식은 시스템의 확장성을 높이고, 단일 JTAG 포트를 통해 다수의 장치를 효율적으로 제어할 수 있게 한다.

데이지 체인 구조

- JTAG 장치의 TDO 출력이 다음 장치의 TDI 입력으로 연결된다.

- 첫 번째 장치는 호스트 디바이스(JTAG 디버거)와 연결되고, 마지막 장치의 TDO는 디버거로 반환된다.

| 장치 이름 | TDI 입력 | TDO 출력 |

|---|---|---|

| 장치 1 | JTAG 디버거 입력 | 장치 2의 TDI 입력 |

| 장치 2 | 장치 1의 TDO 출력 | 장치 3의 TDI 입력 |

| 장치 3 | 장치 2의 TDO 출력 | 디버거로 반환 |

활용 사례

- PCB 테스트: 하나의 JTAG 포트를 통해 보드 상의 모든 장치를 테스트

- 멀티프로세서 디버깅: 여러 마이크로컨트롤러를 연결하여 동시 디버깅 가능

한계와 개선 방안

- 데이터 전송 지연: 장치가 많아질수록 데이터 지연이 발생

- 신호 손실: 연결이 길어질수록 신호 무결성 유지가 어려움

- 솔루션: 고품질 케이블 사용, 신호 증폭기 추가, 장치 수 제한

3. JTAG의 주요 활용 사례

3.1 임베디드 시스템 디버깅

역할과 필요성

JTAG은 임베디드 시스템 디버깅에서 핵심적인 역할을 한다. 임베디드 환경에서는 디버깅을 위한 전통적인 접근법(소프트웨어 디버거 사용)이 어려운 경우가 많다. JTAG는 하드웨어 레벨에서 직접적으로 CPU, 메모리, 그리고 주변 장치의 상태를 읽고 쓸 수 있는 기능을 제공한다.

주요 기능

- 레지스터 및 메모리 액세스: CPU 레지스터 값을 실시간으로 확인하고 수정 가능

- 브레이크포인트 설정: 소스 코드에 없는 부분에서도 실행을 중단하고 상태를 점검

- 실행 흐름 추적: 프로그램 실행 흐름을 단계별로 확인하며 문제를 식별

예제: STM32 기반 디버깅

- JTAG 디버거 연결: STM32 개발 보드의 JTAG 포트를 디버거(예: ST-Link, Segger J-Link)에 연결

- 디버거 소프트웨어 실행: Keil, IAR 등과 같은 IDE에서 JTAG 디버깅 기능 활성화

- 실시간 변수 확인: 실행 중 레지스터 값을 확인하고 변경하며 문제 원인을 분석

JTAG 디버깅은 임베디드 시스템의 문제 해결 시간을 단축시키고, 하드웨어와 소프트웨어 통합 과정의 신뢰성을 높인다.

3.2 펌웨어 업로드와 장치 프로그래밍

역할과 필요성

펌웨어 업로드는 JTAG의 또 다른 주요 활용 사례이다. JTAG를 통해 플래시 메모리에 안전하고 빠르게 펌웨어를 업로드할 수 있으며, 하드웨어 오류로 인해 시스템이 부팅되지 않을 때도 유용하다.

주요 프로세스

- 펌웨어 업로드: 플래시 메모리에 직접적으로 펌웨어를 기록

- 검증 및 읽기: 업로드된 펌웨어가 손상되지 않았는지 확인

- 플래시 초기화: 기존 데이터를 지우고 새 데이터를 기록

예제: OpenOCD를 이용한 펌웨어 업로드

# OpenOCD 구성 파일 로드

openocd -f interface/stlink.cfg -f target/stm32f1x.cfg

# 플래시 메모리에 펌웨어 업로드

program firmware.bin verify reset exit응용 분야

- 공장 생산 라인: JTAG를 사용해 다수의 장치에 펌웨어를 신속하게 업로드

- 현장 유지보수: 손상된 펌웨어를 복구하거나 새로운 펌웨어를 설치

3.3 하드웨어 검증 및 테스트

역할과 필요성

JTAG는 하드웨어 검증 및 테스트에서도 널리 사용된다. Boundary Scan Test(BST)를 통해 회로 보드의 배선 상태와 구성 요소의 기능을 자동으로 확인할 수 있다.

주요 기능

- 배선 연결 상태 테스트: PCB의 핀 간 연결 상태를 확인하여 단선이나 단락을 감지

- IC 기능 검증: 반도체 칩의 동작 상태를 테스트하여 하드웨어 결함 여부를 판단

- 자동화 테스트 지원: JTAG 도구를 사용해 대량의 하드웨어를 자동으로 테스트

Boundary Scan Test 동작 예

- JTAG 명령어 EXTEST를 사용해 외부 핀 상태를 제어

- 입력 핀에 신호를 전송하고, 출력 핀에서 해당 신호를 읽어 배선 상태 검증

- 문제가 감지되면 결함 위치를 보고서로 생성

| 기능 | 목적 | 활용 예 |

|---|---|---|

| 배선 연결 상태 테스트 | PCB 핀 간의 연결 확인 | 제조 공정 중 회로 오류 검출 |

| IC 기능 검증 | IC 내부 동작 상태 검증 | 새로운 칩 설계 검증 |

| 자동화 테스트 | 테스트 절차를 자동화하여 효율성 증가 | 공장 대량 생산 라인 |

JTAG를 활용한 하드웨어 검증 및 테스트는 회로 보드의 초기 품질을 보장하고, 제조 공정에서의 오류를 신속히 식별하는 데 중요한 역할을 한다.

4. JTAG와 보안

4.1 JTAG 인터페이스의 보안 취약점

JTAG의 보안 문제

JTAG 인터페이스는 하드웨어 디버깅과 테스트를 위한 강력한 도구이지만, 보안 관점에서 여러 가지 심각한 취약점을 가진다. 특히, 디바이스 제조사가 기본 보안 설정을 하지 않거나 인터페이스를 열어둔 경우 공격자가 이를 악용할 수 있다.

주요 취약점

- 인증 및 접근 제어 부족: 많은 디바이스에서 JTAG 인터페이스에 대한 접근 인증이 설정되지 않음.

- JTAG 인터페이스 노출: PCB에서 JTAG 핀이 외부에 드러나 있으면 공격자가 쉽게 접근 가능.

- 권한 에스컬레이션: JTAG를 통해 관리자 수준의 접근 권한을 획득하여 시스템을 제어할 수 있음.

- 펌웨어 추출 및 역공학: JTAG를 통해 플래시 메모리에서 펌웨어를 추출한 뒤, 이를 분석해 취약점을 찾거나 민감한 데이터를 도출.

예시

- IoT 장치: 저비용 IoT 장치에서 기본 보안 설정 없이 JTAG 포트를 열어 둔 경우, 공격자가 디바이스를 조작하거나 민감한 정보를 유출할 수 있음.

- 산업용 장치: 산업 제어 시스템(ICS)에서 JTAG 인터페이스가 보호되지 않으면, 공격자가 전체 공정 제어 시스템을 중단시키는 데 사용할 수 있음.

4.2 JTAG 접근 제어 및 잠금 방법

JTAG 보안을 강화하는 방법

JTAG 인터페이스의 보안을 유지하기 위해 제조사와 개발자는 다양한 보호 메커니즘을 구현할 수 있다.

1. JTAG 잠금 및 디세이블 기능

- JTAG 잠금: 디바이스에서 JTAG 인터페이스를 기본적으로 비활성화하고, 특정 조건에서만 활성화되도록 설정

- OTP(One-Time Programmable) 플래그: JTAG를 한 번 비활성화하면 재활성화할 수 없도록 설계

2. JTAG 접근 인증

- JTAG 인터페이스 접근 시 암호 또는 디지털 인증서를 요구

- HMAC 기반 인증 방식을 도입하여 강력한 인증 체계 구축

3. 물리적 보안

- PCB에서 JTAG 핀을 숨기거나 비공개 형태로 제작

- 특정 테스트 모드에서만 JTAG를 활성화하도록 설정

4. 펌웨어 암호화

- JTAG를 통해 펌웨어가 추출되더라도 암호화된 상태로 저장되도록 설정

- 추출된 데이터가 역공학되지 않도록 보호

실제 적용 사례

- Qualcomm 프로세서: Qualcomm은 디바이스 생산 단계에서 JTAG를 잠그고, 개발 중에만 잠금 해제 키를 제공

- Secure Boot: JTAG를 통해 시스템을 공격하지 못하도록 Secure Boot 메커니즘과 연동하여 보호

4.3 JTAG 활용 공격 기법과 방어 전략

공격 기법

JTAG는 공격자가 시스템에 깊이 접근할 수 있는 강력한 도구가 될 수 있다.

-

JTAG 핀 프로빙

- PCB 상의 JTAG 핀에 직접 접근하여 인터페이스를 활성화

- 공격자는 범용 디버거(예: OpenOCD)와 연결하여 데이터를 추출하거나 시스템을 조작

-

펌웨어 추출 및 역공학

- JTAG를 통해 플래시 메모리에서 펌웨어를 읽고, 이를 분석해 취약점을 탐색

-

권한 에스컬레이션

- JTAG를 통해 관리자 권한을 얻어 민감한 시스템 리소스에 접근

-

메모리 변조

- 런타임 동안 메모리 값을 조작하여 시스템 동작을 변경

방어 전략

-

JTAG 핀 비활성화

- 제조 단계에서 JTAG 핀을 기본적으로 비활성화

- 특정 조건에서만 활성화되도록 설정(예: 개발 모드에서만 사용)

-

침입 탐지 시스템(IDS)

- JTAG 포트를 통해 발생하는 비정상적인 액세스를 실시간으로 감지

-

암호화된 데이터 전송

- JTAG 인터페이스에서 암호화된 데이터를 전송하여 공격자가 데이터의 내용을 이해하지 못하도록 보호

-

로그 모니터링

- JTAG 사용 기록을 로그로 저장하고, 이상 징후를 분석하여 사전 경고

방어 솔루션의 실제 활용

- NXP의 Secure JTAG: NXP는 보안 인증을 통해서만 JTAG 접근을 허용하는 기능을 도입

- TrustZone 통합: ARM의 TrustZone 기술은 JTAG와 같은 디버깅 인터페이스를 분리된 보안 영역에서 관리하여 민감한 데이터 접근을 방지

5. JTAG 사용 및 실습

5.1 JTAG 디버거 도구 소개 (OpenOCD, Segger J-Link 등)

주요 JTAG 디버거 도구

- OpenOCD

- 오픈소스 JTAG 디버거로, 다양한 프로세서와 마이크로컨트롤러를 지원

- 강력한 커뮤니티 지원과 사용자 정의 가능한 설정 파일 제공

- 주요 기능: 플래시 메모리 프로그래밍, 디버깅, 레지스터 액세스

예시: OpenOCD 명령어

openocd -f interface/stlink.cfg -f target/stm32f1x.cfg-

Segger J-Link

- 상용 디버거 도구로, 빠르고 안정적인 디버깅과 프로그래밍 환경을 제공

- Segger의 J-Flash 유틸리티를 통해 GUI 기반의 디버깅 지원

- 주요 기능: 실시간 디버깅, 메모리 쓰기/읽기, 프로세서 실행 제어

-

Keil ULINK

- Keil IDE와 통합된 디버거로, Cortex-M 계열 마이크로컨트롤러를 효과적으로 지원

- 사용자가 쉽게 접근 가능한 GUI 환경과 다양한 디버깅 옵션 제공

디버거 선택 기준

| 기준 | OpenOCD | Segger J-Link | Keil ULINK |

|---|---|---|---|

| 가격 | 무료 | 유료 | 유료 |

| 호환성 | 다양한 플랫폼 지원 | Segger 지원 칩셋에 최적화 | Cortex-M 계열에 특화 |

| 사용자 인터페이스 | CLI 중심 | GUI 제공 | GUI 제공 |

5.2 JTAG 설정과 테스트 방법

JTAG 설정 단계

-

하드웨어 연결

- 디바이스의 JTAG 핀(TDI, TDO, TCK, TMS, GND)을 디버거 장치와 연결

- 연결 오류 방지를 위해 핀 매칭을 정확히 확인

-

소프트웨어 환경 설정

- OpenOCD와 같은 디버깅 소프트웨어 설치 및 설정 파일 작성

- 예: STM32 디바이스를 위한 설정 파일

source [find interface/stlink.cfg]

source [find target/stm32f1x.cfg]

init

reset halt- 디버거 테스트

- 연결 성공 시 디버거 CLI에 접근 가능

- 디버깅 연결 상태 확인:

openocd -f interface/stlink.cfg -f target/stm32f1x.cfg

telnet localhost 4444- 기본 명령 테스트

- 레지스터 읽기, 메모리 쓰기

mdw 0x20000000

mww 0x20000000 0xDEADBEEF6. 마무리

직접 하드웨어를 만져본 적이 없어서 그런지, 좀 생소한 개념들이 많았다. 다음주 쯤엔 직접 실습해볼 수 있으리라 생각하니 기대된다.